# 16-Bit, ±0.5 LSB, 500 kSPS PulSAR® Differential ADC in MSOP/LFCSP

Data Sheet AD7693

#### **FEATURES**

16-bit resolution with no missing codes

Throughput: 500 kSPS

INL/DNL:  $\pm 0.25$  LSB typ,  $\pm 0.5$  LSB max ( $\pm 8$  ppm of FSR)

Dynamic range: 96.5 dB SINAD: 96 dB at 1 kHz THD: –120 dB at 1 kHz

True differential analog input range: ±VREF 0 V to VREF with VREF up to VDD on both inputs

No pipeline delay

Single-supply 5 V operation with 1.8 V/2.5 V/3 V/5 V logic interface

**Proprietary serial interface**

SPI®-/QSPI™-/MICROWIRE™-/DSP-compatible1

Daisy-chain multiple ADCs, selectable busy indicator

Power dissipation: 40 nJ/conversion

40 μW at 5 V/1 kSPS 4 mW at 5 V/100 kSPS 18 mW at 5 V/500 kSPS Standby current: 1 nA

10-lead package: MSOP (MSOP-8 size) and 3 mm × 3 mm LFCSP (SOT-23 size)

Pin-for-pin compatible with the 16-bit AD7687 and AD7688

and the 18-bit AD7690 and AD7691

#### **APPLICATIONS**

**Medical instruments**

Battery-powered equipment

Data acquisitions

Seismic data acquisition systems

DVMs

Instrumentation

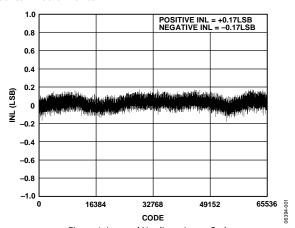

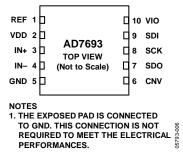

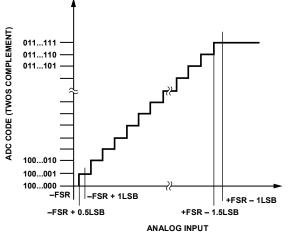

Figure 1. Integral Nonlinearity vs. Code

# Rev. B Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

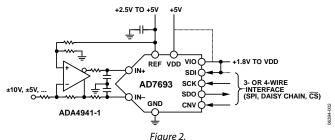

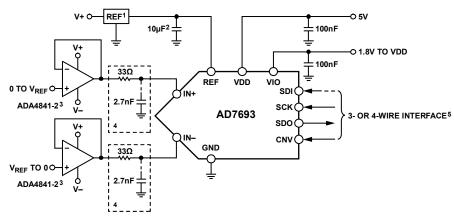

#### **APPLICATION DIAGRAM**

Table 1. MSOP, LFCSP/SOT-23 14-/16-/18-Bit PulSAR ADC

|                             |             |             | 400 kSPS         |                        |

|-----------------------------|-------------|-------------|------------------|------------------------|

| Туре                        | 100<br>kSPS | 250<br>kSPS | to<br>500 kSPS   | ADC<br>Driver          |

| 18-Bit                      |             | AD7691      | AD7690           | ADA4941-1<br>ADA4841-x |

| 16-Bit True<br>Differential | AD7684      | AD7687      | AD7688<br>AD7693 | ADA4941-1<br>ADA4841-x |

| 16-Bit Pseudo               | AD7683      | AD7685      | AD7686           | ADA4841-x              |

| Differential/<br>Unipolar   | AD7680      | AD7694      |                  |                        |

| 14-Bit                      | AD7940      | AD7942      | AD7946           | ADA4841-x              |

#### **GENERAL DESCRIPTION**

The AD7693 is a 16-bit, successive approximation analog-to-digital converter (ADC) that operates from a single power supply, VDD. It contains a low power, high speed, 16-bit sampling ADC with no missing codes, an internal conversion clock, and a versatile serial interface port. The reference voltage,  $V_{\rm REF}$ , is applied externally and can be set up to the supply voltage, VDD. On the CNV rising edge, it samples the voltage difference between the IN+ and IN– pins. The voltages on these pins swing in opposite phase between 0 V and  $V_{\rm REF}$  about  $V_{\rm REF}/2$ .

Its power scales linearly with throughput.

Using the SDI input, the SPI-compatible serial interface also features the ability to daisy-chain several ADCs on a single 3-wire bus and provides an optional busy indicator. It is compatible with  $1.8\ V, 2.5\ V, 3\ V,$  or  $5\ V$  logic, using the separate VIO supply.

The AD7693 is housed in a 10-lead MSOP or a 10-lead LFCSP with operation specified from  $-40^{\circ}$ C to  $+85^{\circ}$ C.

<sup>&</sup>lt;sup>1</sup> Protected by U.S. Patent 6,703,961.

# AD7693\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

## COMPARABLE PARTS $\Box$

View a parametric search of comparable parts.

## **EVALUATION KITS**

- · AD7693 Evaluation Kit

- Precision ADC PMOD Compatible Boards

## **DOCUMENTATION**

#### **Application Notes**

- AN-742: Frequency Domain Response of Switched-Capacitor ADCs

- AN-931: Understanding PulSAR ADC Support Circuitry

- AN-932: Power Supply Sequencing

#### **Data Sheet**

AD7693: 16-Bit, ±0.5 LSB, 500 kSPS PulSAR® Differential ADC in MSOP/LFCSP Data Sheet

#### **Technical Books**

The Data Conversion Handbook, 2005

#### **User Guides**

- UG-340: Evaluation Board for the 10-Lead Family 14-/16-/ 18-Bit PulSAR ADCs

- UG-682: 6-Lead SOT-23 ADC Driver for the 8-/10-Lead Family of 14-/16-/18-Bit PulSAR ADC Evaluation Boards

## SOFTWARE AND SYSTEMS REQUIREMENTS 🖵

- AD7693 FMC-SDP Interposer & Evaluation Board / Xilinx KC705 Reference Design

- BeMicro FPGA Project for AD7693 with Nios driver

## **TOOLS AND SIMULATIONS** $\Box$

· AD7685 IBIS Models

## REFERENCE MATERIALS 🖵

#### **Product Selection Guide**

SAR ADC & Driver Ouick-Match Guide

#### **Technical Articles**

- MS-1779: Nine Often Overlooked ADC Specifications

- MS-2210: Designing Power Supplies for High Speed ADC

#### Tutorials

- MT-002: What the Nyquist Criterion Means to Your Sampled Data System Design

- MT-074: Differential Drivers for Precision ADCs

## DESIGN RESOURCES 🖵

- · AD7693 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

## **DISCUSSIONS**

View all AD7693 EngineerZone Discussions.

## SAMPLE AND BUY 🖵

Visit the product page to see pricing options.

## TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

## **TABLE OF CONTENTS**

| Features                                                | Driver Amplifier Choice                         | 14 |

|---------------------------------------------------------|-------------------------------------------------|----|

| Applications1                                           | Single-Ended-to-Differential Driver             | 15 |

| Application Diagram1                                    | Voltage Reference Input                         | 15 |

| General Description                                     | Power Supply                                    | 15 |

| Revision History                                        | Supplying the ADC from the Reference            | 16 |

| Specifications                                          | Digital Interface                               | 16 |

| Timing Specifications                                   | CS Mode, 3-Wire Without Busy Indicator          | 17 |

| Absolute Maximum Ratings6                               | CS Mode, 3-Wire with Busy Indicator             | 18 |

| ESD Caution6                                            | CS Mode, 4-Wire Without Busy Indicator          | 19 |

| Pin Configurations and Function Descriptions7           | CS Mode, 4-Wire with Busy Indicator             |    |

| Terminology8                                            | Chain Mode Without Busy Indicator               |    |

| Typical Performance Characteristics                     | Chain Mode with Busy Indicator                  |    |

| Theory of Operation                                     | Application Hints                               |    |

| Circuit Information                                     | Layout                                          |    |

| Converter Operation12                                   | Evaluating AD7693 Performance                   |    |

| Typical Connection Diagram13                            | Outline Dimensions                              |    |

| Analog Inputs14                                         | Ordering Guide                                  |    |

| REVISION HISTORY                                        |                                                 |    |

| 6/14—Rev. A to Rev. B                                   | 6/11—Rev. 0 to Rev. A                           |    |

| Added Patent Footnote                                   | Changes to Resolution Parameter and Common-Mode | -  |

| Changes to Evaluating the AD7693 Performance Section 23 | Range Parameter in Table 2                      |    |

| Updated Outline Dimensions (Dimensions Not Changed;     | Changes to Figure 6 and Table 6                 | 7  |

| Lead-to-Pad Dimensions Updated for JEDEC Compliance) 24 | Updated Outline Dimensions                      | 24 |

12/06—Revision 0: Initial Version

## **SPECIFICATIONS**

VDD = 4.5 V to 5.5 V, VIO = 2.3 V to VDD,  $V_{REF} = VDD$ , all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 2.

| Parameter                               | Conditions/Comments                               | Min               | Тур         | Max               | Unit             |

|-----------------------------------------|---------------------------------------------------|-------------------|-------------|-------------------|------------------|

| RESOLUTION                              |                                                   | 16                |             |                   | Bits             |

| ANALOG INPUT                            |                                                   |                   |             |                   |                  |

| Voltage Range                           | IN+ - (IN-)                                       | $-V_{REF}$        |             | $+V_{REF}$        | V                |

| Absolute Input Voltage                  | IN+, IN-                                          | -0.1              |             | $V_{REF} + 0.1$   | V                |

| Common-Mode Input Range                 | IN+, IN-                                          | $V_{REF}/2 - 0.1$ | $V_{REF}/2$ | $V_{REF}/2 + 0.1$ | V                |

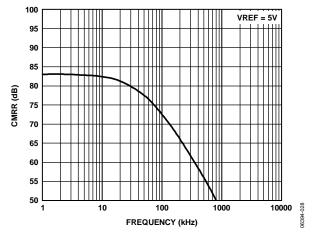

| Analog Input CMRR                       | $f_{IN} = 250 \text{ kHz}$                        |                   | 65          |                   | dB               |

| Leakage Current at 25°C                 | Acquisition phase                                 |                   | 1           |                   | nA               |

| Input Impedance <sup>1</sup>            |                                                   |                   |             |                   |                  |

| THROUGHPUT                              |                                                   |                   |             |                   |                  |

| Conversion Rate                         |                                                   | 0                 |             | 500               | kSPS             |

| Transient Response                      | Full-scale step                                   |                   |             | 400               | ns               |

| ACCURACY                                |                                                   |                   |             |                   |                  |

| No Missing Codes                        |                                                   | 16                |             |                   | Bits             |

| Integral Linearity Error                |                                                   | -0.5              | ±0.25       | +0.5              | LSB <sup>2</sup> |

| Differential Linearity Error            |                                                   | -0.5              | ±0.25       | +0.5              | LSB              |

| Transition Noise                        | REF = VDD = 5 V                                   |                   | 0.35        |                   | LSB              |

| Gain Error <sup>3</sup>                 |                                                   | -20               | ±0.5        | +20               | LSB              |

| Gain Error Temperature Drift            |                                                   |                   | ±0.3        |                   | ppm/°C           |

| Zero Error <sup>3</sup>                 |                                                   | <b>-5</b>         | ±0.5        | +5                | LSB              |

| Zero Temperature Drift                  |                                                   |                   | ±0.3        |                   | ppm/°C           |

| Power Supply Sensitivity                | $VDD = 5 V \pm 5\%$                               |                   | ±1          |                   | ppm              |

| AC ACCURACY⁴                            |                                                   |                   |             |                   |                  |

| Dynamic Range                           |                                                   | 96                | 96.5        |                   | dB⁵              |

| Signal-to-Noise                         | $f_{IN} = 1 \text{ kHz}$                          | 95.5              | 96          |                   | dB               |

|                                         | $f_{IN} = 10 \text{ kHz}$                         |                   | 95.5        |                   | dB               |

|                                         | $f_{IN} = 100 \text{ kHz}$                        |                   | 93          |                   | dB               |

|                                         | $f_{IN} = 1 \text{ kHz}, V_{REF} = 2.5 \text{ V}$ |                   | 93          |                   | dB               |

| Signal-to-(Noise + Distortion)          | $f_{IN} = 1 \text{ kHz}$                          | 95.5              | 96          |                   | dB               |

|                                         | $f_{IN} = 10 \text{ kHz}$                         |                   | 95.5        |                   | dB               |

|                                         | $f_{\text{IN}} = 100 \text{ kHz}$                 |                   | 90          |                   | dB               |

| Total Harmonic Distortion               | $f_{IN} = 1 \text{ kHz}$                          |                   | -120        | -108              | dB               |

|                                         | $f_{IN} = 10 \text{ kHz}$                         |                   | -113        |                   | dB               |

|                                         | $f_{IN} = 100 \text{ kHz}$                        |                   | -92         |                   | dB               |

| Spurious-Free Dynamic Range             | $f_{IN} = 1 \text{ kHz}$                          |                   | 120         |                   | dB               |

|                                         | $f_{IN} = 10 \text{ kHz}$                         |                   | 114         |                   | dB               |

|                                         | $f_{IN} = 100 \text{ kHz}$                        |                   | 93.5        |                   | dB               |

| Intermodulation Distortion <sup>6</sup> |                                                   |                   | 115         |                   | dB               |

$<sup>^1</sup>$  See the Analog Inputs section.  $^2$  LSB means least significant bit. With the  $\pm 5$  V input range, one LSB is 152.6  $\mu$ V.  $^3$  See the Terminology section. These specifications include full temperature range variation but not the error contribution from the external reference.

$<sup>^4</sup>$  With  $V_{REF} = 5$  V, unless otherwise noted.

<sup>5</sup> All specifications expressed in decibels are referred to a full-scale input FSR and tested with an input signal at 0.5 dB below full scale, unless otherwise specified.

$<sup>^6</sup>$  f<sub>IN1</sub> = 21.4 kHz and f<sub>IN2</sub> = 18.9 kHz, with each tone at -7 dB below full scale.

VDD = 4.5 V to 5.5 V, VIO = 2.3 V to VDD,  $V_{REF} = VDD$ , all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 3.

| Parameter                       | Conditions/Comments                  | Min       | Тур | Max               | Unit |

|---------------------------------|--------------------------------------|-----------|-----|-------------------|------|

| REFERENCE                       |                                      |           | ·   |                   |      |

| Voltage Range                   |                                      | 0.5       |     | VDD + 0.3         | V    |

| Load Current                    | 500 kSPS, REF = 5 V                  |           | 100 |                   | μΑ   |

| SAMPLING DYNAMICS               |                                      |           |     |                   |      |

| -3 dB Input Bandwidth           |                                      |           | 9   |                   | MHz  |

| Aperture Delay                  | VDD = 5V                             |           | 2.5 |                   | ns   |

| DIGITAL INPUTS                  |                                      |           |     |                   |      |

| Logic Levels                    |                                      |           |     |                   |      |

| $V_{IL}$                        |                                      | -0.3      |     | $+0.3 \times VIO$ | V    |

| V <sub>IH</sub>                 |                                      | 0.7 × VIO |     | VIO + 0.3         | V    |

| I <sub>IL</sub>                 |                                      | -1        |     | +1                | μΑ   |

| Iн                              |                                      | -1        |     | +1                | μΑ   |

| DIGITAL OUTPUTS                 |                                      |           |     |                   |      |

| Data Format                     | Serial 16 bits, twos                 |           |     |                   |      |

| Pipeline Delay <sup>1</sup>     | complement                           |           |     |                   |      |

| V <sub>OL</sub>                 | $I_{SINK} = +500 \mu A$              |           |     | 0.4               | V    |

| $V_{OH}$                        | $I_{SOURCE} = -500 \mu\text{A}$      | VIO - 0.3 |     |                   | V    |

| POWER SUPPLIES                  |                                      |           |     |                   |      |

| VDD                             | Specified performance                | 4. 5      |     | 5.5               | V    |

| VIO                             | Specified performance                | 2.3       |     | VDD + 0.3         | V    |

| VIO Range                       |                                      | 1.8       |     | VDD + 0.3         | V    |

| Standby Current <sup>2, 3</sup> | VDD and VIO = 5 V, 25°C              |           | 1   | 50                | nA   |

| Power Dissipation               | 100 SPS throughput                   |           | 5   |                   | μW   |

|                                 | 100 kSPS throughput                  |           | 4   |                   | mW   |

|                                 | 500 kSPS throughput                  |           | 18  | 21.5              | mW   |

| Energy per Conversion           |                                      |           | 40  |                   | nJ   |

| TEMPERATURE RANGE⁴              |                                      |           |     |                   |      |

| Specified Performance           | T <sub>MIN</sub> to T <sub>MAX</sub> | -40       |     | +85               | °C   |

Conversion results available immediately after completed conversion.

With all digital inputs forced to VIO or GND as required.

During acquisition phase.

Contact an Analog Devices sales representative for the extended temperature range.

## TIMING SPECIFICATIONS

VDD = 4.5 V to 5.5 V, VIO = 2.3 V to VDD,  $V_{REF} = VDD$ , all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 4.1

| Parameter                                                                | Symbol               | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------|----------------------|-----|-----|-----|------|

| Conversion Time: CNV Rising Edge to Data Available                       | t <sub>CONV</sub>    | 0.5 |     | 1.6 | μs   |

| Acquisition Time                                                         | t <sub>ACQ</sub>     | 400 |     |     | ns   |

| Time Between Conversions                                                 | <b>t</b> cyc         | 2.0 |     |     | μs   |

| CNV Pulse Width (CS Mode)                                                | tcnvh                | 10  |     |     | ns   |

| SCK Period (CS Mode)                                                     | t <sub>SCK</sub>     | 15  |     |     | ns   |

| SCK Period (Chain Mode)                                                  | t <sub>SCK</sub>     |     |     |     |      |

| VIO Above 4.5 V                                                          |                      | 17  |     |     | ns   |

| VIO Above 3 V                                                            |                      | 18  |     |     | ns   |

| VIO Above 2.7 V                                                          |                      | 19  |     |     | ns   |

| VIO Above 2.3 V                                                          |                      | 20  |     |     | ns   |

| SCK Low Time                                                             | tsckl                | 7   |     |     | ns   |

| SCK High Time                                                            | <b>t</b> sckH        | 7   |     |     | ns   |

| SCK Falling Edge to Data Remains Valid                                   | t <sub>HSDO</sub>    | 4   |     |     | ns   |

| SCK Falling Edge to Data Valid Delay                                     | t <sub>DSDO</sub>    |     |     |     |      |

| VIO Above 4.5 V                                                          |                      |     |     | 14  | ns   |

| VIO Above 3 V                                                            |                      |     |     | 15  | ns   |

| VIO Above 2.7 V                                                          |                      |     |     | 16  | ns   |

| VIO Above 2.3 V                                                          |                      |     |     | 17  | ns   |

| CNV or SDI Low to SDO D15 MSB Valid (CS Mode)                            | t <sub>EN</sub>      |     |     |     |      |

| VIO Above 4.5 V                                                          |                      |     |     | 15  | ns   |

| VIO Above 2.7 V                                                          |                      |     |     | 18  | ns   |

| VIO Above 2.3 V                                                          |                      |     |     | 22  | ns   |

| CNV or SDI High or Last SCK Falling Edge to SDO High Impedance (CS Mode) | t <sub>DIS</sub>     |     |     | 25  | ns   |

| SDI Valid Setup Time from CNV Rising Edge (CS Mode)                      | t <sub>SSDICNV</sub> | 15  |     |     | ns   |

| SDI Valid Hold Time from CNV Rising Edge (CS Mode)                       | t <sub>HSDICNV</sub> | 0   |     |     | ns   |

| SCK Valid Setup Time from CNV Rising Edge (Chain Mode)                   | tssckcnv             | 5   |     |     | ns   |

| SCK Valid Hold Time from CNV Rising Edge (Chain Mode)                    | thsckcnv             | 10  |     |     | ns   |

| SDI Valid Setup Time from SCK Falling Edge (Chain Mode)                  | tssdisck             | 4   |     |     | ns   |

| SDI Valid Hold Time from SCK Falling Edge (Chain Mode)                   | thsdisck             | 4   |     |     | ns   |

| SDI High to SDO High (Chain Mode with Busy Indicator)                    | t <sub>DSDOSDI</sub> |     |     |     |      |

| VIO Above 4.5 V                                                          |                      |     |     | 15  | ns   |

| VIO Above 2.3 V                                                          |                      |     |     | 26  | ns   |

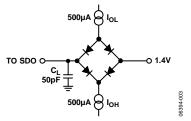

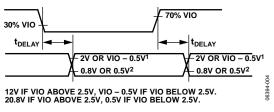

<sup>&</sup>lt;sup>1</sup> See Figure 3 and Figure 4 for load conditions.

## **ABSOLUTE MAXIMUM RATINGS**

Table 5.

| Parameter                                 | Rating                                |

|-------------------------------------------|---------------------------------------|

| Analog Inputs                             |                                       |

| IN+, <sup>1</sup> IN- <sup>1</sup>        | GND - 0.3 V to VDD + 0.3 V or ±130 mA |

| REF                                       | GND - 0.3 V to VDD + 0.3 V            |

| Supply Voltages                           |                                       |

| VDD, VIO to GND                           | −0.3 V to +7 V                        |

| VDD to VIO                                | ±7 V                                  |

| Digital Inputs to GND                     | −0.3 V to VIO + 0.3 V                 |

| Digital Outputs to GND                    | −0.3 V to VIO + 0.3 V                 |

| Storage Temperature Range                 | −65°C to +150°C                       |

| Junction Temperature                      | 150°C                                 |

| $\theta_{JA}$ Thermal Impedance (MSOP-10) | 200°C/W                               |

| $\theta_{JC}$ Thermal Impedance (MSOP-10) | 44°C/W                                |

| Lead Temperature Range                    | JEDEC J-STD-20                        |

<sup>&</sup>lt;sup>1</sup> See the Analog Inputs section.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

Figure 3. Load Circuit for Digital Interface Timing

Figure 4. Voltage Levels for Timing

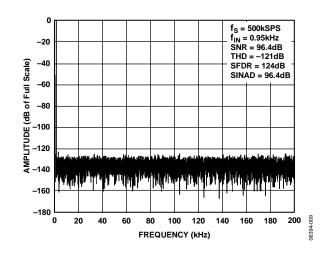

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 5. 10-Lead MSOP Pin Configuration

Figure 6. 10-Lead LFCSP Pin Configuration

**Table 6. Pin Function Descriptions**

| Pin No. | Mnemonic | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | REF      | Al                | Reference Input Voltage. The REF range is from 0.5 V to VDD. It is referred to the GND pin. This pin should be decoupled closely to the pin with a 10 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2       | VDD      | Р                 | Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3       | IN+      | Al                | Differential Positive Analog Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4       | IN-      | Al                | Differential Negative Analog Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5       | GND      | Р                 | Power Supply Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6       | CNV      | DI                | Convert Input. This input has multiple functions. On its leading edge, it initiates the conversions and selects the interface mode of the part: chain or CS mode. In chain mode, the data should be read when CNV is high. In CS mode, the SDO pin is enabled when CNV is low.                                                                                                                                                                                                                                                                                                                                                             |

| 7       | SDO      | DO                | Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8       | SCK      | DI                | Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9       | SDI      | DI                | Serial Data Input. This input provides multiple features. It selects the interface mode of the ADC as follows:  Chain mode is selected if SDI is low during the CNV rising edge. In this mode, SDI is used as a data input to daisy-chain the conversion results of two or more ADCs onto a single SDO line.  The digital data level on SDI is output on SDO with a delay of 16 SCK cycles.  CS mode is selected if SDI is high during the CNV rising edge. In this mode, either SDI or CNV can enable the serial output signals when low and if SDI or CNV is low when the conversion is complete, the busy indicator feature is enabled. |

| 10      | VIO      | P                 | Input/Output Interface Digital Power. Nominally at the same supply as the host interface (1.8 V, 2.5 V, 3 V, or 5 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | EPAD     |                   | Exposed Pad. The exposed pad is connected to GND. This connection is not required to meet the electrical performances. The exposed pad is only on the 10-Lead LFCSP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

$<sup>^{1}</sup>AI = analog input$ , DI = digital input, DO = digital output, and P = power.

### **TERMINOLOGY**

#### Least Significant Bit (LSB)

The LSB is the smallest increment that can be represented by a converter. For a differential analog-to-digital converter with N bits of resolution, the LSB expressed in volts is

$$LSB(V) = \frac{2V_{REF}}{2^N}$$

#### **Integral Nonlinearity Error (INL)**

INL refers to the deviation of each individual code from a line drawn from negative full scale through positive full scale. The point used as negative full scale occurs ½ LSB before the first code transition. Positive full scale is defined as a level 1½ LSB beyond the last code transition. The deviation is measured from the middle of each code to the true straight line (see Figure 26).

#### Differential Nonlinearity Error (DNL)

In an ideal ADC, code transitions are 1 LSB apart. DNL is the maximum deviation from this ideal value. It is often specified in terms of resolution for which no missing codes are guaranteed.

#### Zero Error

Zero error is the difference between the ideal midscale voltage, that is, 0 V, from the actual voltage producing the midscale output code, that is, 0 LSB.

#### **Gain Error**

The first transition (from  $100 \dots 00$  to  $100 \dots 01$ ) should occur at a level ½ LSB above nominal negative full scale (-4.999847 V for the  $\pm 5$  V range). The last transition (from  $011 \dots 10$  to  $011 \dots 11$ ) should occur for an analog voltage  $1\frac{1}{2}$  LSB below the nominal full scale (+4.999771 V for the  $\pm 5$  V range.) The gain error is the deviation of the difference between the actual level of the last transition and the actual level of the first transition from the difference between the ideal levels.

#### **Aperture Delay**

Aperture delay is the measure of the acquisition performance. It is the time between the rising edge of the CNV input and when the input signal is held for a conversion.

#### **Transient Response**

Transient response is the time required for the ADC to accurately acquire its input after a full-scale step function is applied.

#### **Dynamic Range**

Dynamic range is the ratio of the rms value of the full scale to the total rms noise measured with the inputs shorted together. The value for dynamic range is expressed in decibels.

#### Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below the Nyquist frequency, excluding harmonics and dc. The value for SNR is expressed in decibels.

#### Signal-to-(Noise + Distortion) Ratio (SINAD)

SINAD is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for SINAD is expressed in decibels.

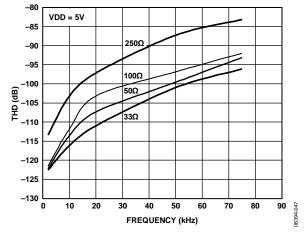

#### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of the first five harmonic components to the rms value of a full-scale input signal and is expressed in decibels.

#### Spurious-Free Dynamic Range (SFDR)

SFDR is the difference, in decibels, between the rms amplitude of the input signal and the peak spurious signal.

#### Effective Number of Bits (ENOB)

ENOB is a measurement of the resolution with a sine wave input. It is related to SINAD by the following formula:

$$ENOB = (SINAD_{dB} - 1.76)/6.02$$

and is expressed in bits.

## TYPICAL PERFORMANCE CHARACTERISTICS

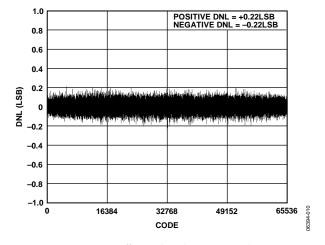

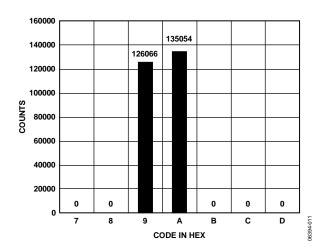

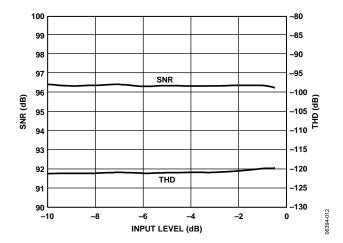

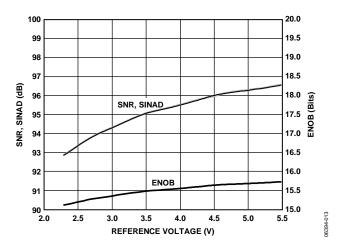

VDD = 4.5 V to 5.5 V, VIO = 2.3 V to VDD,  $V_{REF}$  = VDD,  $T_A$  = 25°C.

Figure 7. Integral Nonlinearity vs. Code

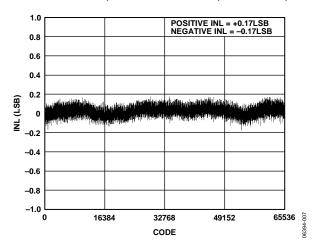

Figure 8. Histogram of a DC Input at the Code Center

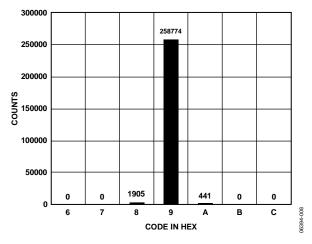

Figure 9. FFT Plot

Figure 10. Differential Nonlinearity vs. Code

Figure 11. Histogram of a DC Input at the Code Transition

Figure 12. SNR, THD vs. Input Level

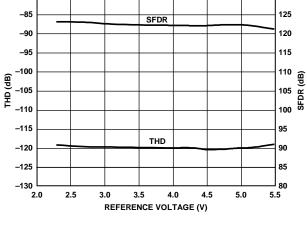

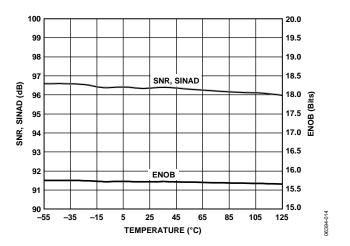

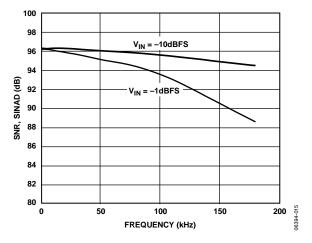

Figure 13. SNR, SINAD, and ENOB vs. Reference Voltage

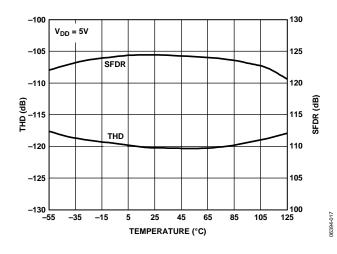

Figure 16. THD, SFDR vs. Reference Voltage

Figure 14. SNR, SINAD, and ENOB vs. Temperature

Figure 17. THD, SFDR vs. Temperature

Figure 15. SINAD vs. Frequency

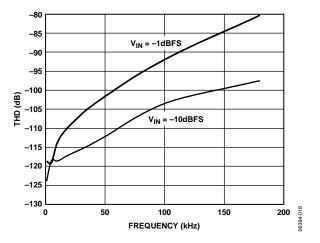

Figure 18. THD vs. Frequency

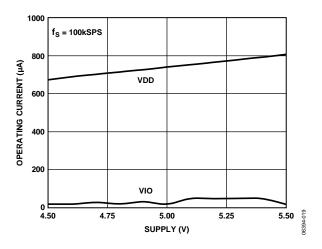

Figure 19. Operating Currents vs. Supply

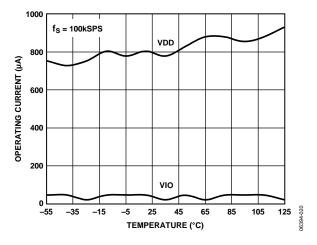

Figure 20. Operating Currents vs. Temperature

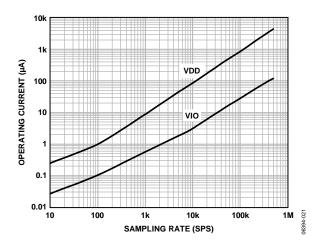

Figure 21. Operating Currents vs. Sample Rate

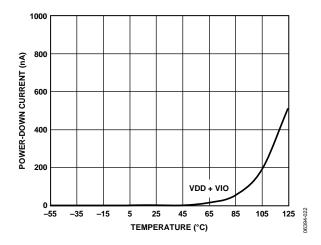

Figure 22. Power-Down Currents vs. Temperature

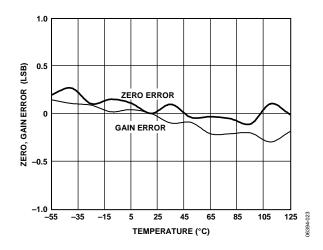

Figure 23. Zero Error and Gain Error vs. Temperature

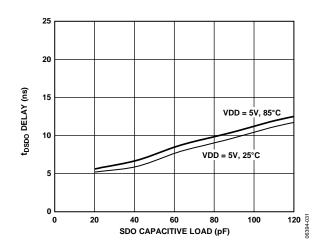

Figure 24. t<sub>DSDO</sub> Delay vs. Capacitance Load and Supply

### THEORY OF OPERATION

#### CIRCUIT INFORMATION

The AD7693 is a fast, low power, single-supply, precise, 16-bit ADC using a successive approximation architecture.

The AD7693 is capable of converting 500,000 samples per second (500 kSPS) and powers down between conversions. When operating at 1 kSPS, for example, it consumes 40  $\mu$ W typically, ideal for battery-powered applications.

The AD7693 provides the user with an on-chip track-and-hold and does not exhibit pipeline delay or latency, making it ideal for multiple multiplexed channel applications.

The AD7693 is specified from 4.5 V to 5.5 V and can be interfaced to any 1.8 V to 5 V digital logic family. It is housed in a 10-lead MSOP or a tiny 10-lead LFCSP that combines space savings and allows flexible configurations.

It is pin-for-pin compatible with the 16-bit AD7687 and AD7688 and with the 18-bit AD7690 and AD7691.

#### **CONVERTER OPERATION**

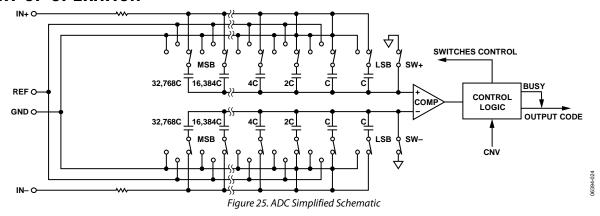

The AD7693 is a successive approximation ADC based on a charge redistribution DAC. Figure 25 shows the simplified schematic of the ADC. The capacitive DAC consists of two identical arrays of 16 binary-weighted capacitors, which are connected to the two comparator inputs.

During the acquisition phase, terminals of the array tied to the comparator's input are connected to GND via SW+ and SW-. All independent switches are connected to the analog inputs.

Thus, the capacitor arrays are used as sampling capacitors and acquire the analog signal on the IN+ and IN- inputs. When the acquisition phase is complete and the CNV input goes high, a conversion phase is initiated. When the conversion phase begins, SW+ and SW- are opened first. The two capacitor arrays are then disconnected from the inputs and connected to the GND input. Therefore, the differential voltage between the IN+ and IN- inputs captured at the end of the acquisition phase is applied to the comparator inputs, causing the comparator to become unbalanced. By switching each element of the capacitor array between GND and REF, the comparator input varies by binary-weighted voltage steps (V<sub>REF</sub>/2, V<sub>REF</sub>/4 ... V<sub>REF</sub>/32,768). The control logic toggles these switches, starting with the MSB, to bring the comparator back into a balanced condition. After the completion of this process, the part returns to the acquisition phase, and the control logic generates the ADC output code and a busy signal indicator.

Because the AD7693 has an on-board conversion clock, the serial clock, SCK, is not required for the conversion process.

#### **Transfer Functions**

The ideal transfer characteristic for the AD7693 is shown in Figure 26 and Table 7.

Figure 26. ADC Ideal Transfer Function

Table 7. Output Codes and Ideal Input Voltages

| Description      | Analog Input<br>V <sub>REF</sub> = 5 V | Digital Output<br>Code (Hex) |

|------------------|----------------------------------------|------------------------------|

| FSR – 1 LSB      | +4.999847 V                            | 0x7FFF <sup>1</sup>          |

| Midscale + 1 LSB | +152.6 μV                              | 0x0001                       |

| Midscale         | 0 V                                    | 0x0000                       |

| Midscale – 1 LSB | –152.6 μV                              | 0xFFFF                       |

| −FSR + 1 LSB     | -4.999847 V                            | 0x8001                       |

| –FSR             | −5 V                                   | 0x8000 <sup>2</sup>          |

<sup>&</sup>lt;sup>1</sup> This is also the code for an overranged analog input ( $V_{IN+} - V_{IN-}$  above  $V_{REF} - V_{GND}$ ).

#### **TYPICAL CONNECTION DIAGRAM**

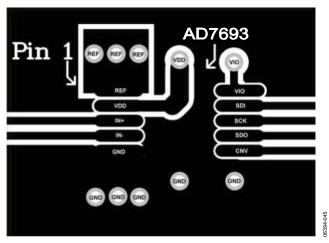

Figure 27 shows an example of the recommended connection diagram for the AD7693 when multiple supplies are available.

<sup>1</sup>SEE REFERENCE SECTION FOR REFERENCE SELECTION. <sup>2</sup>C<sub>REF</sub> IS USUALLY A 10µF CERAMIC CAPACITOR (X5R). <sup>3</sup>SEE TABLE 8 FOR ADDITIONAL RECOMMENDED AMPLIFIERS.

40PTIONAL FILTER. SEE ANALOG INPUT SECTION.

5SEE THE DIGITAL INTERFACE SECTION FOR MOST CONVENIENT INTERFACE MODE.

Figure 27. Typical Application Diagram with Multiple Supplies

<sup>&</sup>lt;sup>2</sup> This is also the code for an underranged analog input  $(V_{IN+} - V_{IN-} \text{ below } V_{GND})$ .

#### **ANALOG INPUTS**

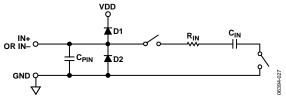

Figure 28 shows an equivalent circuit of the input structure of the AD7693.

The two diodes, D1 and D2, provide ESD protection for the analog inputs, IN+ and IN-. Care must be taken to ensure that the analog input signal does not exceed the supply rails by more than 0.3 V because this causes the diodes to become forward biased and to start conducting current. These diodes can handle a forward-biased current of 130 mA maximum. For instance, these conditions could eventually occur when the input buffer's (U1) supplies are different from VDD. In such a case, for example, an input buffer with a short circuit, the current limitation can be used to protect the part.

Figure 28. Equivalent Analog Input Circuit

The analog input structure allows the sampling of the true differential signal between IN+ and IN-. By using these differential inputs, signals common to both inputs are rejected.

Figure 29. Analog Input CMRR vs. Frequency

During the acquisition phase, the impedance of the analog inputs (IN+ and IN–) can be modeled as a parallel combination of the capacitor,  $C_{\text{PIN}}$ , and the network formed by the series connection of  $R_{\text{IN}}$  and  $C_{\text{IN}}$ .  $C_{\text{PIN}}$  is primarily the pin capacitance.  $R_{\text{IN}}$  is typically 600  $\Omega$  and is a lumped component made up of serial resistors and the on resistance of the switches.  $C_{\text{IN}}$  is typically 30 pF and is mainly the ADC sampling capacitor.

During the conversion phase, where the switches are opened, the input impedance is limited to  $C_{PIN}$ .  $R_{IN}$  and  $C_{IN}$  make a 1-pole, low-pass filter that reduces undesirable aliasing effects and limits the noise.

When the source impedance of the driving circuit is low, the AD7693 can be driven directly. Large source impedances significantly affect the ac performance, especially total

harmonic distortion (THD). The dc performances are less sensitive to the input impedance. The maximum source impedance depends on the amount of THD that can be tolerated. The THD degrades as a function of the source impedance and the maximum input frequency.

Figure 30. THD vs. Analog Input Frequency and Source Resistance

#### **DRIVER AMPLIFIER CHOICE**

Although the AD7693 is easy to drive, the driver amplifier must meet the following requirements:

• The noise generated by the driver amplifier needs to be kept as low as possible to preserve the SNR and transition noise performance of the AD7693. The noise coming from the driver is filtered by the AD7693 analog input circuit's 1-pole, low-pass filter made by  $R_{\rm IN}$  and  $C_{\rm IN}$  or by the external filter, if one is used. Because the typical noise of the AD7693 is 56  $\mu$ V rms, the SNR degradation due to the amplifier is

$$SNR_{LOSS} = 20 \log \left( \frac{56}{\sqrt{56^2 + \frac{\pi}{2} f_{-3 \text{dB}} (Ne_N)^2 + \frac{\pi}{2} f_{-3 \text{dB}} (Ne_N)^2}} \right)$$

where:

$f_{-3 \text{ dB}}$  is the input bandwidth in megahertz of the AD7693 (9 MHz) or the cutoff frequency of the input filter, if one is used.

N is the noise gain of the amplifier (for example, 1 in buffer configuration).

$e_N$  is the equivalent input noise voltage of the op amp, in nV/ $\sqrt{\text{Hz}}$ .

- For ac applications, the driver should have a THD performance commensurate with the AD7693.

- For multichannel multiplexed applications, the driver amplifier and the AD7693 analog input circuit must settle for a full-scale step onto the capacitor array at a 16-bit level (0.0015%, 15 ppm). In the amplifier's data sheet, settling at 0.1% to 0.01% is more commonly specified. This could differ significantly from the settling time at a 16-bit level and should be verified prior to driver selection.

**Table 8. Recommended Driver Amplifiers**

| Amplifier      | Typical Application                              |

|----------------|--------------------------------------------------|

| ADA4941-1      | Very low noise, low power single to differential |

| ADA4841-x      | Very low noise, small, and low power             |

| AD8655         | 5 V single supply, low noise                     |

| AD8021         | Very low noise and high frequency                |

| AD8022         | Low noise and high frequency                     |

| OP184          | Low power, low noise, and low frequency          |

| AD8605, AD8615 | 5 V single supply, low power                     |

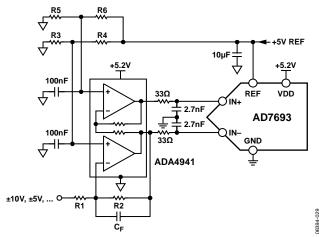

#### SINGLE-ENDED-TO-DIFFERENTIAL DRIVER

For applications using a single-ended analog signal, either bipolar or unipolar, the ADA4941-1 single-ended-to-differential driver allows for a differential input into the part. The schematic is shown in Figure 31.

R1 and R2 set the attenuation ratio between the input range and the ADC range (V<sub>REF</sub>). R1, R2, and C<sub>F</sub> are chosen depending on the desired input resistance, signal bandwidth, antialiasing and noise contribution. For example, for the  $\pm 10$  V range with a 4 k $\Omega$  impedance, R2 = 1 k $\Omega$  and R1 = 4 k $\Omega$ .

R3 and R4 set the common mode on the IN– input, and R5 and R6 set the common mode on the IN+ input of the ADC. The common mode should be set close to  $V_{\text{REF}}/2$ ; however, if single supply is desired, it can be set slightly above  $V_{\text{REF}}/2$  to provide some headroom for the ADA4941-1 output stage. For example, for the  $\pm 10$  V range with a single supply, R3 = 8.45 k $\Omega$ , R4 = 11.8 k $\Omega$ , R5 = 10.5 k $\Omega$ , and R6 = 9.76 k $\Omega$ .

Figure 31. Single-Ended-to-Differential Driver Circuit

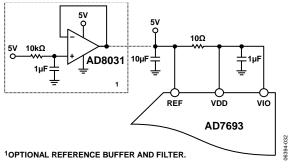

#### **VOLTAGE REFERENCE INPUT**

The AD7693 voltage reference input, REF, has a dynamic input impedance and should therefore be driven by a low impedance source with efficient decoupling between the REF and GND pins, as explained in the Layout section.

When REF is driven by a very low impedance source (for example, a reference buffer using the AD8031 or the AD8605), a  $10~\mu F$  (X5R, 0805 size) ceramic chip capacitor is appropriate for optimum performance.

If an unbuffered reference voltage is used, the decoupling value depends on the reference used. For instance, a 22  $\mu F$  (X5R, 1206 size) ceramic chip capacitor is appropriate for optimum performance using low temperature drift ADR43x and ADR44x references.

If desired, smaller reference decoupling capacitor values down to 2.2  $\mu F$  can be used with a minimal impact on performance, especially DNL.

Regardless, there is no need for an additional lower value ceramic decoupling capacitor (for example, 100 nF) between the REF and GND pins.

#### **POWER SUPPLY**

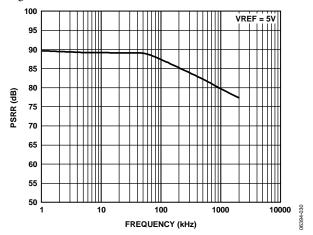

The AD7693 uses two power supply pins: a core supply, VDD, and a digital input/output interface supply, VIO. VIO allows direct interface with any logic between 1.8 V and VDD. To reduce the supplies needed, the VIO and VDD pins can be tied together. The AD7693 is independent of power supply sequencing between VIO and VDD. Additionally, it is very insensitive to power supply variations over a wide frequency range, as shown in Figure 32.

Figure 32. PSRR vs. Frequency

The AD7693 powers down automatically at the end of each conversion phase; therefore, the operating currents and power scale linearly with the sampling rate (refer to Figure 21). This makes the part ideal for low sampling rates (even of a few hertz) and low battery-powered applications.

#### SUPPLYING THE ADC FROM THE REFERENCE

For simplified applications, the AD7693, with its low operating current, can be supplied directly using the reference circuit shown in Figure 33. The reference line can be driven by

- The system power supply directly

- A reference voltage with enough current output capability, such as the ADR43x

- A reference buffer, such as the AD8031, which can also filter the system power supply, as shown in Figure 33.

Figure 33. Example of an Application Circuit

#### **DIGITAL INTERFACE**

Generally, a user is interested in either minimizing the wiring complexity of a multichannel ADC system or communicating with the parts via a specific interface standard. Although the ADC has only four digital pins (CNV, SCK, SDI, and SDO), it offers a significantly flexible serial interface, including compatibility with SPI, QSPI, digital hosts, and DSPs (such as Blackfin\* ADSP-BF53x or ADSP-219x). By configuring the ADC into one of six modes, virtually any serial interface scenario can be accommodated.

For wiring efficiency, the best way to configure a multichannel, simultaneous-sampling system is to use the 3-wire chain mode. This system is easily created by cascading multiple (M) ADCs into a shift register structure. The CNV and CLK pins are common to all ADCs, and the SDO of one part feeds the SDI of the next part in the chain. The 3-wire interface is simply the CNV, SCK, and SDO of the last ADC in the chain. For a system containing M- and N-bit converters, the user needs to provide  $M \times N$  SCK transitions to read back all of the data. This 3-wire interface is also ideally suited for isolated applications.

Additional flexibility is provided by optionally configuring the ADCs to provide a busy indication. Without a busy indication, the user must externally timeout the maximum ADC conversion time before commencing readback. This configuration is described in the Chain Mode Without Busy Indicator section. With the busy indication enabled, external timer circuits are not required because the SDO at the end of the chain provides a low-to-high transition (that is, a start bit) when all of the chain members have completed their conversions and are ready to transmit data. However, one additional SCK is required to flush the SDO busy

indication prior to reading back the data. This configuration is described in the Chain Mode with Busy Indicator section.

The primary limitations of 3-wire chain mode are that all ADCs are simultaneously sampled and the user cannot randomly select an individual ADC for readback. This can be overcome only by increasing the number of wires (for example, one chip select wire per ADC). To operate with this increased functionality, the part must be used in  $\overline{CS}$  Mode.  $\overline{CS}$  mode is separated into two categories (3-wire and 4-wire) whereby flexibility is traded off for wiring complexity. In  $\overline{CS}$  4-wire mode, the user has independent control over the sampling operation (via CNV) and the chip select operation (via SDI) for each ADC. In  $\overline{\text{CS}}$  3-wire mode, SDI is unused (tied high) and CNV is used to both sample the input and chip select the part when needed. As with chain mode, the parts can optionally be configured to provide a busy indication, but at the expense of one additional SCK when reading back the data. So in total there are four  $\overline{CS}$  modes: 3-wire and 4-wire modes, each with busy and without busy.

There is no elaborate writing of configuration words into the part via the SDI pin. The mode in which the part operates is defined by ensuring a specific relationship between the CNV, SDI, and SCK inputs at key times. To select  $\overline{CS}$  mode, ensure that SDI is high at the rising edge of CNV; otherwise, chain mode will be selected. Once in  $\overline{CS}$  mode, selecting the part for readback *before* the conversion is complete (by bringing either SDI or CNV low) instructs the part to provide a busy indicator, a high-to-low impedance transition on SDO, to tell the user when the conversion has finished. If the part is selected *after* the conversion has finished, SDO outputs the MSB when it is selected. In chain mode, the busy indicator, a low-to-high transition on SDO, is selected based on the state of SCK at the rising edge of CNV. If SCK is high, the busy indicator is enabled; otherwise, the busy indicator is not enabled.

The following sections provide specifics for each of the different serial interface modes. Note that in the following sections, the timing diagrams indicate digital activity (SCK, CNV) during conversion. However, due to the possibility of performance degradation, digital activity should only occur during the first quarter of the conversion phase because the AD7693 provides error correction circuitry that can correct for an incorrect bit during this time. The user should initiate the busy indicator if desired during this time. It is also possible to corrupt the sample by having SCK or SDI transitions near the sampling instant. Therefore, it is recommended to keep the digital pins quiet for approximately 30 ns before and 10 ns after the rising edge of CNV. The exception is when the device is in the chain mode with busy configuration, where SDI is tied to CNV, because this scenario does not yield a corrupted sample. To this extent, it is recommended, to use a discontinuous SCK whenever possible to avoid any potential performance degradation.

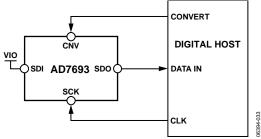

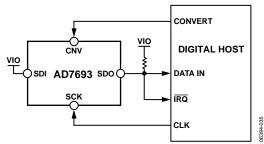

## **CS MODE, 3-WIRE WITHOUT BUSY INDICATOR**

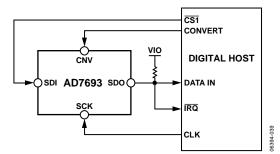

This mode is usually used when a single AD7693 is connected to an SPI-compatible digital host. The connection diagram is shown in Figure 34, and the corresponding timing is given in Figure 35.

With SDI tied to VIO, a rising edge on CNV initiates a conversion, selects the  $\overline{\text{CS}}$  mode, and forces SDO to high impedance. Once a conversion is initiated, it continues until completion irrespective of the state of CNV. This could be useful, for instance, to bring CNV low to select other SPI devices, such as analog multiplexers; however, CNV must be

returned high before the minimum conversion time elapses and then held high for the maximum possible conversion time to avoid the generation of the busy signal indicator. When the conversion is complete, the AD7693 enters the acquisition phase and powers down. When CNV goes low, the MSB is output onto SDO. The remaining data bits are clocked by subsequent SCK falling edges. The data is valid on both SCK edges. Although the rising edge can be used to capture the data, a digital host using the SCK falling edge will allow a faster reading rate, provided it has an acceptable hold time. After the 16th SCK falling edge or when CNV goes high (whichever occurs first), SDO returns to high impedance.

Figure 34. CS Mode, 3-Wire Without Busy Indicator Connection Diagram (SDI High)

Figure 35. CS Mode, 3-Wire Without Busy Indicator Serial Interface Timing (SDI High)

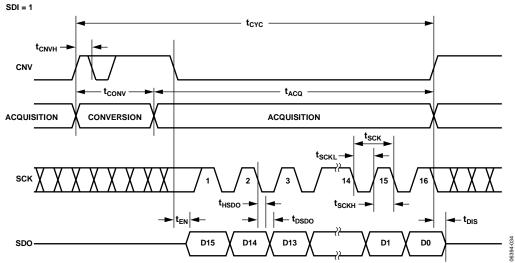

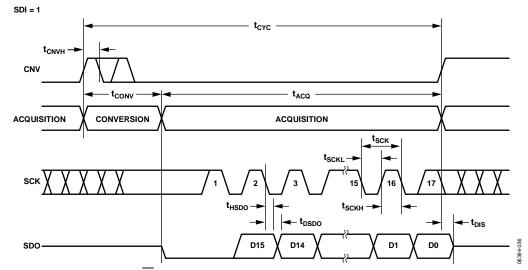

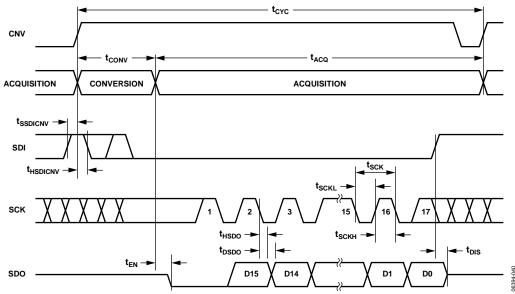

#### **CS MODE, 3-WIRE WITH BUSY INDICATOR**

This mode is usually used when a single AD7693 is connected to an SPI-compatible digital host having an interrupt input.

The connection diagram is shown in Figure 36, and the corresponding timing is given in Figure 37.

With SDI tied to VIO, a rising edge on CNV initiates a conversion, selects the  $\overline{\text{CS}}$  mode, and forces SDO to high impedance. SDO is maintained in high impedance until the completion of the conversion irrespective of the state of CNV. Prior to the minimum conversion time, CNV can be used to select other SPI devices, such as analog multiplexers, but CNV must be returned low before the minimum conversion time elapses and then held low for the maximum possible conversion time to guarantee the generation of the busy signal indicator. When the conversion is complete, SDO goes from high

impedance to low impedance. With a pull-up on the SDO line, this transition can be used as an interrupt signal to initiate the data reading controlled by the digital host. The AD7693 then enters the acquisition phase and powers down. The data bits are clocked out, MSB first, by subsequent SCK falling edges. The data is valid on both SCK edges. Although the rising edge can be used to capture the data, a digital host using the SCK falling edge will allow a faster reading rate, provided it has an acceptable hold time. After the optional 17th SCK falling edge or when CNV goes high (whichever occurs first), SDO returns to high impedance.

If multiple AD7693s are selected at the same time, the SDO output pin handles this contention without damage or induced latch-up. Meanwhile, it is recommended to keep this contention as short as possible to limit extra power dissipation.

Figure 36. CS Mode, 3-Wire with Busy Indicator Connection Diagram (SDI High)

Figure 37. CS Mode, 3-Wire with Busy Indicator Serial Interface Timing (SDI High)

#### **CS MODE, 4-WIRE WITHOUT BUSY INDICATOR**

This mode is usually used when multiple AD7693s are connected to an SPI-compatible digital host.

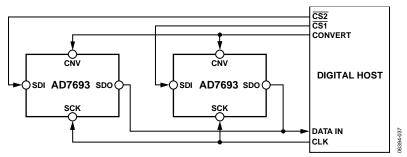

A connection diagram example using two AD7693s is shown in Figure 38, and the corresponding timing is given in Figure 39.

With SDI high, a rising edge on CNV initiates a conversion, selects the  $\overline{\text{CS}}$  mode, and forces SDO to high impedance. In this mode, CNV must be held high during the conversion phase and the subsequent data readback. (If SDI and CNV are low, SDO is driven low.) Prior to the minimum conversion time, SDI can be used to select other SPI devices, such as analog multiplexers, but SDI must be returned high before the minimum conversion time

elapses and then held high for the maximum possible conversion time to avoid the generation of the busy signal indicator. When the conversion is complete, the AD7693 enters the acquisition phase and powers down. Each ADC result can be read by bringing its SDI input low, which consequently outputs the MSB onto SDO. The remaining data bits are clocked by subsequent SCK falling edges. The data is valid on both SCK edges. Although the rising edge can be used to capture the data, a digital host using the SCK falling edge will allow a faster reading rate, provided it has an acceptable hold time. After the 16<sup>th</sup> SCK falling edge or when SDI goes high (whichever occurs first), SDO returns to high impedance and another AD7693 can be read.

Figure 38. CS Mode, 4-Wire Without Busy Indicator Connection Diagram

Figure 39. CS Mode, 4-Wire Without Busy Indicator Serial Interface Timing

#### **CS MODE, 4-WIRE WITH BUSY INDICATOR**

This mode is usually used when a single AD7693 is connected to an SPI-compatible digital host with an interrupt input and it is desired to keep CNV, which is used to sample the analog input, independent of the signal used to select the data reading. This requirement is particularly important in applications where low jitter on CNV is desired.

The connection diagram is shown in Figure 40, and the corresponding timing is given in Figure 41.

With SDI high, a rising edge on CNV initiates a conversion, selects the  $\overline{\text{CS}}$  mode, and forces SDO to high impedance. In this mode, CNV must be held high during the conversion phase and the subsequent data readback. (If SDI and CNV are low, SDO is driven low.) Prior to the minimum conversion time, SDI can be used to select other SPI devices, such as analog multiplexers,

but SDI must be returned low before the minimum conversion time elapses and then held low for the maximum possible conversion time to guarantee the generation of the busy signal indicator. When the conversion is complete, SDO goes from high impedance to low impedance. With a pull-up on the SDO line, this transition can be used as an interrupt signal to initiate the data readback controlled by the digital host. The AD7693 then enters the acquisition phase and powers down. The data bits are clocked out, MSB first, by subsequent SCK falling edges. The data is valid on both SCK edges. Although the rising edge can be used to capture the data, a digital host using the SCK falling edge will allow a faster reading rate, provided it has an acceptable hold time. After the optional 17th SCK falling edge, or when SDI goes high (whichever occurs first), SDO returns to high impedance.

Figure 40. CS Mode, 4-Wire with Busy Indicator Connection Diagram

Figure 41. CS Mode, 4-Wire with Busy Indicator Serial Interface Timing

#### **CHAIN MODE WITHOUT BUSY INDICATOR**

This mode can be used to daisy-chain multiple AD7693s on a 3-wire serial interface. This feature is useful for reducing component count and wiring connections, for example, in isolated multiconverter applications or for systems with a limited interfacing capacity. Data readback is analogous to clocking a shift register.

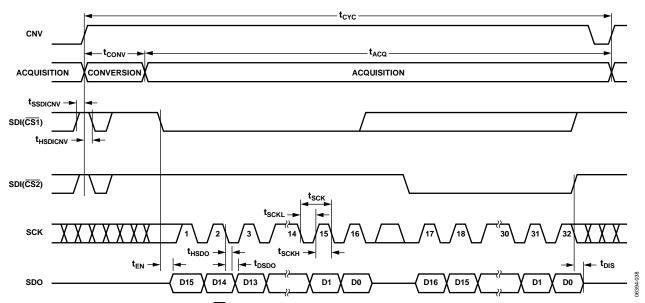

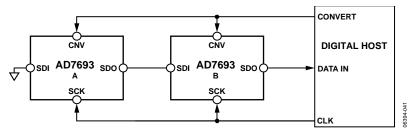

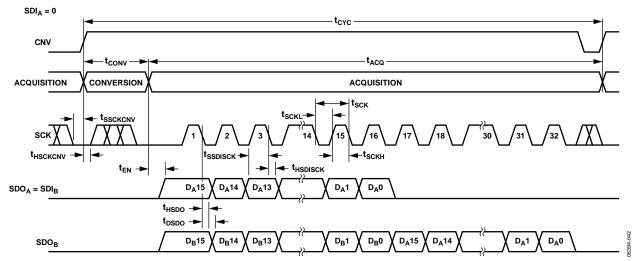

A connection diagram example using two AD7693s is shown in Figure 42, and the corresponding timing is given in Figure 43.

When SDI and CNV are low, SDO is driven low. With SCK low, a rising edge on CNV initiates a conversion, selects the chain mode, and disables the busy indicator. In this mode, CNV is held high during the conversion phase and the subsequent data

readback. When the conversion is complete, the MSB is output onto SDO and the AD7693 enters the acquisition phase and powers down. The remaining data bits stored in the internal shift register are clocked by subsequent SCK falling edges. For each ADC, SDI feeds the input of the internal shift register and is clocked by the SCK falling edge. Each ADC in the chain outputs its data MSB first, and  $16 \times N$  clocks are required to read back the N ADCs. The data is valid on both SCK edges. Although the rising edge can be used to capture the data, a digital host using the SCK falling edge will allow a faster reading rate and consequently more AD7693s in the chain, provided the digital host has an acceptable hold time. The maximum conversion rate can be reduced due to the total readback time.

Figure 42. Chain Mode Without Busy Indicator Connection Diagram

Figure 43. Chain Mode Without Busy Indicator Serial Interface Timing

#### **CHAIN MODE WITH BUSY INDICATOR**

This mode can also be used to daisy-chain multiple AD7693s on a 3-wire serial interface while providing a busy indicator. This feature is useful for reducing component count and wiring connections, for example, in isolated multiconverter applications or for systems with a limited interfacing capacity. Data readback is analogous to clocking a shift register.

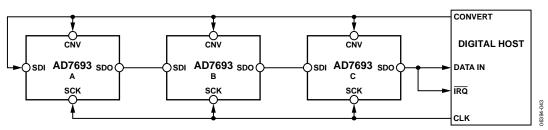

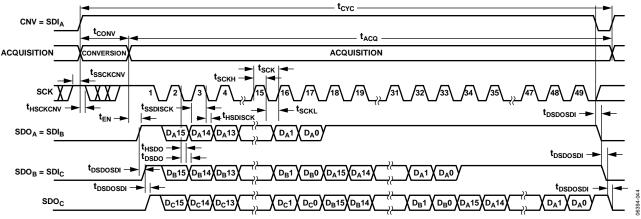

A connection diagram example using three AD7693s is shown in Figure 44, and the corresponding timing is given in Figure 45.

When SDI and CNV are low, SDO is driven low. With SCK high, a rising edge on CNV initiates a conversion, selects the chain mode, and enables the busy indicator feature. In this mode, CNV is held high during the conversion phase and the subsequent data readback. When all ADCs in the chain have

completed their conversions, the SDO pin of the ADC closest to the digital host (see the AD7693 ADC labeled C in Figure 44) is driven high. This transition on SDO can be used as a busy indicator to trigger the data readback controlled by the digital host. The AD7693 then enters the acquisition phase and powers down. The data bits stored in the internal shift register are clocked out, MSB first, by subsequent SCK falling edges. For each ADC, SDI feeds the input of the internal shift register and is clocked by the SCK falling edge. Each ADC in the chain outputs its data MSB first, and  $16 \times N + 1$  clocks are required to readback the N ADCs. Although the rising edge can be used to capture the data, a digital host using the SCK falling edge allows a faster reading rate and consequently more AD7693s in the chain, provided the digital host has an acceptable hold time.

Figure 44. Chain Mode with Busy Indicator Connection Diagram

Figure 45. Chain Mode with Busy Indicator Serial Interface Timing

## **APPLICATION HINTS**

#### **LAYOUT**

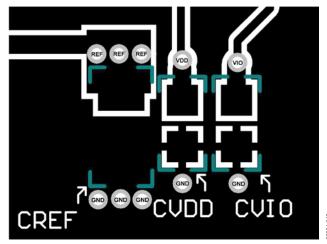

The printed circuit board that houses the AD7693 should be designed so that the analog and digital sections are separated and confined to certain areas of the board. The pinout of the AD7693, with all its analog signals on the left side and all its digital signals on the right side, eases this task.

Avoid running digital lines under the device because these couple noise onto the die unless a ground plane under the AD7693 is used as a shield. Fast switching signals, such as CNV or clocks, should not run near analog signal paths. Crossover of digital and analog signals should be avoided.

At least one ground plane should be used. It could be common or split between the digital and analog sections. In the latter case, the planes should be joined underneath the AD7693s.

The AD7693 voltage reference input REF has a dynamic input impedance and should be decoupled with minimal parasitic inductances. This is done by placing the reference decoupling ceramic capacitor close to, ideally right up against, the REF and GND pins and connecting them with wide, low impedance traces.

Finally, the power supplies VDD and VIO of the AD7693 should be decoupled with ceramic capacitors, typically 100 nF, placed close to the AD7693 and connected using short, wide traces to provide low impedance paths and reduce the effect of glitches on the power supply lines.

An example of a layout following these rules is shown in Figure 46 and Figure 47.

#### **EVALUATING THE AD7693 PERFORMANCE**

Other recommended layouts for the AD7693 are outlined in the documentation of the evaluation board for the AD7693 (EVAL-AD7693SDZ). The evaluation board package includes a fully assembled and tested evaluation board, documentation, and software for controlling the board from a PC via the EVAL-SDP-CB1Z.

Figure 46. Example Layout of the AD7693 (Top Layer)

Figure 47. Example Layout of the AD7693 (Bottom Layer)

## **OUTLINE DIMENSIONS**

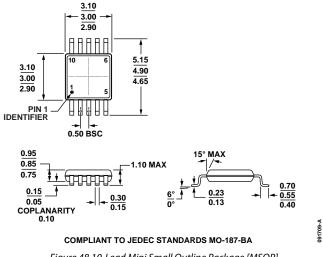

Figure 48.10-Lead Mini Small Outline Package [MSOP] (RM-10)

Dimensions shown in millimeters

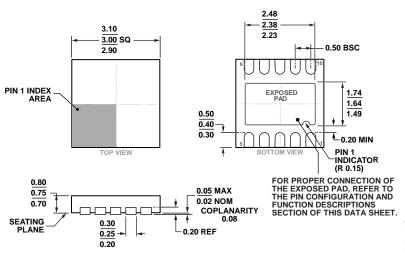

Figure 49. 10-Lead Lead Frame Chip Scale Package [LFCSP\_WD] 3 mm × 3 mm Body, Very Very Thin, Dual Lead (CP-10-9) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1, 2, 3</sup> | Temperature Range | Package Description | Package Option | Branding | Ordering Quantity |

|--------------------------|-------------------|---------------------|----------------|----------|-------------------|

| AD7693BCPZRL             | -40°C to +85°C    | 10-Lead LFCSP_WD    | CP-10-9        | C4Y      | Reel, 5,000       |

| AD7693BCPZRL7            | -40°C to +85°C    | 10-Lead LFCSP_WD    | CP-10-9        | C4Y      | Reel, 1,500       |

| AD7693BRMZ               | -40°C to +85°C    | 10-Lead MSOP        | RM-10          | C4Y      | Tube, 50          |

| AD7693BRMZRL7            | -40°C to +85°C    | 10-Lead MSOP        | RM-10          | C4Y      | Reel, 1,000       |

| EVAL-AD7693SDZ           |                   | Evaluation Board    |                |          |                   |

| EVAL-SDP-CB1Z            |                   | Controller Board    |                |          |                   |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

<sup>&</sup>lt;sup>3</sup> The EVAL-SDP-CB1Z allows a PC to control and communicate with all Analog Devices evaluation boards ending in the SD designator.

<sup>&</sup>lt;sup>2</sup> This board can be used as a standalone evaluation board or in conjunction with the EVAL-SDP-CB1Z for evaluation/demonstration purposes.